# Intel 8251 (USART- Universal Synchronous Asynchronous Receiver Transmitter)

It acts as a mediator between microprocessor and peripheral to transmit serial data into parallel form and vice versa.

- 1. It takes data serially from peripheral (outside devices) and converts into parallel data.

- 2. After converting the data into parallel form, it transmits it to the CPU.

- 3. Similarly, it receives parallel data from microprocessor and converts it into serial form.

- After converting data into serial form, it transmits it to outside device (peripheral).

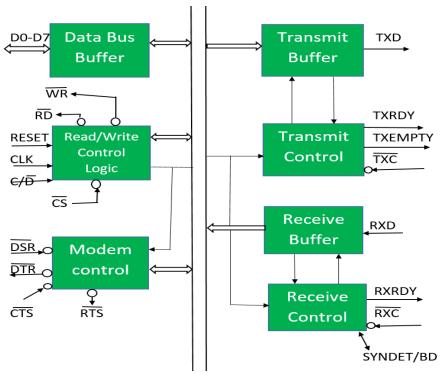

## **Block Diagram of 8251 USART**

It contains the following blocks:

## 1. Data bus buffer -

This block helps in interfacing the internal data bus of 8251 to the system data bus. The data transmission is possible between 8251 and CPU by the data bus buffer block.

## 2. Read/Write control logic -

It is a control block for overall device. It controls the overall working by selecting the operation to be done. The operation selection depends upon input signals as:

The operation selection depends upon input signals as:

| <del>CS</del> | C/D | RD | WR | Operation                 |

|---------------|-----|----|----|---------------------------|

| 1             | Х   | Х  | Х  | Invalid                   |

| 0             | 0   | 0  | 1  | data<br>CPU< 8251         |

| 0             | 0   | 1  | 0  | data<br>CPU > 8251        |

| 0             | 1   | 0  | 1  | Status word<br>CPU <8251  |

| 0             | 1   | 1  | 0  | Control word<br>CPU> 8251 |

In this way, this unit selects one of the three registers- data buffer register, control register, status register.

# 1. Modem control (modulator/demodulator)

A device converts analog signals to digital signals and vice-versa and helps the computers to communicate over telephone lines or cable wires. The following are active-low pins of Modem.

- **DSR:** Data Set Ready signal is an input signal.

- **DTR:** Data terminal Ready is an output signal.

- CTS: It is an input signal which controls the data transmit circuit. RTS: It is an output signal which is used to set the status RTS.

#### 2. Transmit buffer -

This block is used for parallel to serial converter that receives a parallel byte for conversion into serial signal and further transmission onto the common channel.

• **TXD:** It is an output signal, if its value is one, means transmitter will transmit the data.

## 3. Transmit control -

This block is used to control the data transmission with the help of following pins:

- **TXRDY:** It means transmitter is ready to transmit data character.

- **TXEMPTY:** An output signal which indicates that TXEMPTY pin has transmitted all the data characters and transmitter is empty now.

- **TXC:** An active-low input pin which controls the data transmission rate of transmitted data.

## 4. Receive buffer -

This block acts as a buffer for the received data.

• **RXD:** An input signal which receives the data.

## 5. Receive control -

This block controls the receiving data.

- **RXRDY:** An input signal indicates that it is ready to receive the data.

- **RXC:** An active-low input signal which controls the data transmission rate of received data.

- **SYNDET/BD:** An input or output terminal. External synchronous mode-input terminal and asynchronous mode-output terminal.